Le projet européen FASTLANE, coordonné par le chef de file industriel VALEO, et d’un montant total de 90 Mi d’euros pour 3 ans, réunit 21 partenaires à travers l’Europe autour de la chaine de valeur du carbure de silicium SiC.

LE PROJET

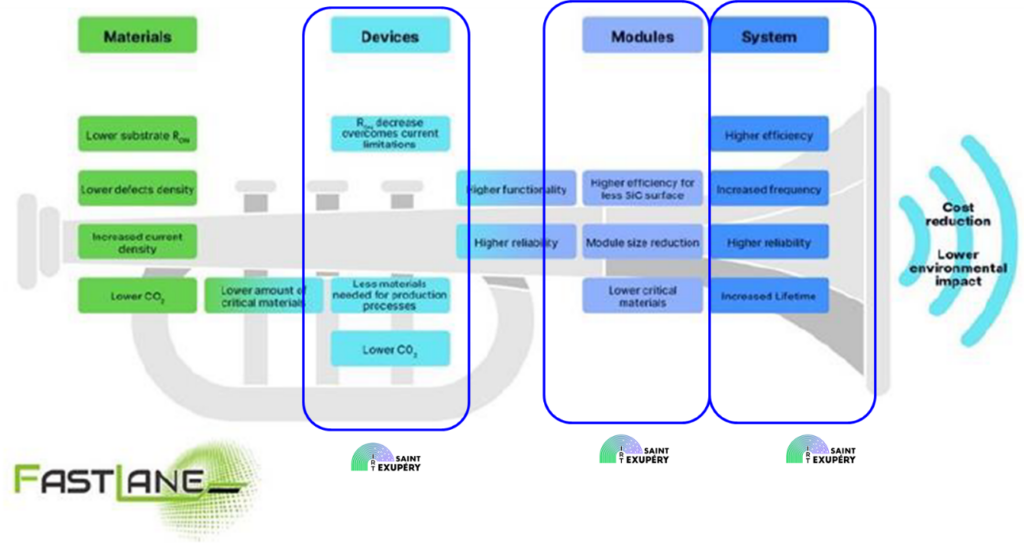

L’objectif de cet ambitieux projet est d’adresser la chaine de valeur complète de la technologie SiC afin de la rendre plus compétitive et durable en Europe.

Du substrat SiC avec l’industriel SOITEC, aux applications onduleur automobile et électrolyseur industriel avec VALEO et BOSCH (voir Figure 1), en passant par les transistors de puissances avec INFINEON : tous les acteurs majeurs de la chaine de valeurs du SiC font preuve d’une grande ingénierie afin de permettre la venue sur le marché de modules d’alimentation et de convertisseurs de puissance intelligents.

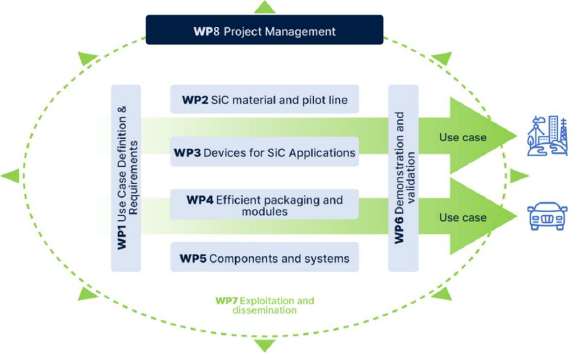

Le projet est divisé en 8 lots, dont 4 portants sur des étapes technologiques incrémentales (voir :Figure 3)

- LOT 2 : les thématiques du matériau SiC pour fabrication de substrat optimisée

- LOT 3 : la fabrication de transistors de puissance SiC avec fonctionnalités avancées

- LOT 4: la conception et fabrication de modules de puissances SiC performants

- LOT 5: l’optimisation du système ou cas d’usage complet.

L’IRT travaillera principalement dans les LOTS 3 4 et 5 avec les apports suivants (voir Figure 3) :

- LOT 3 : retour d’expérience de projet SICRET portant sur la caractérisation des transistors de puissance SiC

- LOT 4 : forte synergie avec le projet SICRET +, suite du projet SICRET, portant sur l’étude des modules de puissance SiC. Expertise sur la caractérisation et modélisation des pertes dans les modules de puissance SiC.

- LOT 5 : expertise sur la caractérisation et l’optimisation de la chaine de traction, synergie avec le projet Repowerdrive portant sur l’optimisation de la chaine de traction complète prenant en compte les contraintes de compatibilité électromagnétiques.

La philosophie générale du projet est d’améliorer la chaine de valeur de la technologie SiC en valorisant au maximum les parties prenantes européennes tout en visant une réduction du coût et de l’empreinte environnementale de la technologie SiC. C’est pour cela qu’un LOT transverse ACV, Analyse du Cycle de Vie, s’attachera à prouver la réduction de l’empreinte environnementale des nouvelles technologies SiC développées dans FASTLANE par rapport aux technologies SiC actuelles, faisant office de référence.

Financé par l’Union européenne. Les points de vue et les opinions exprimés sont toutefois ceux des auteurs et ne reflètent pas nécessairement ceux de l’Union européenne ou de l’entreprise commune Chips. Ni l’Union européenne ni l’autorité chargée de l’octroi des subventions ne peuvent en être tenues pour responsables. Le projet est soutenu par l’entreprise commune Chips et ses membres, y compris un financement complémentaire de l’Autriche, de la France, de l’Allemagne, de la Roumanie et de la Slovaquie, dans le cadre de la convention de subvention n° 101139788.