The European FASTLANE project, coordinated by the industrial leader VALEO, and with a total amount of 90 million euros for 3 years, brings together 21 partners across Europe around the SiC silicon carbide value chain.

THE PROJECT

The objective of this ambitious project is to address the complete value chain of SiC technology in order to make it more competitive and sustainable in Europe.

From the SiC substrate with the industrial SOITEC, to automotive inverter and industrial electrolyser applications with VALEO and BOSCH (see Figure 1), through power transistors with INFINEON: all the major players in the SiC value chain demonstrate great engineering to enable the arrival on the market of intelligent power modules and power converters.

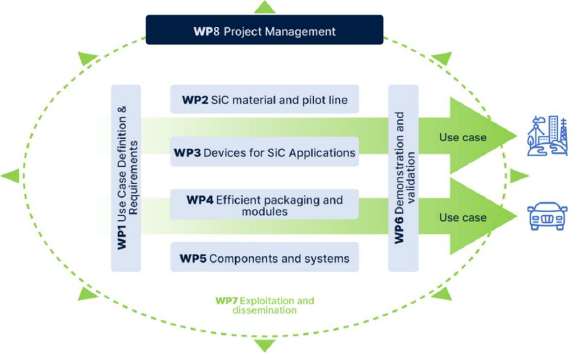

The project is divided into 8 work packages WP, 4 of which relate to incremental technological steps (see Figure 2)

- WP 2: SiC material for optimized substrate manufacturing

- WP 3: manufacturing of SiC power transistors with advanced functionalities

- WP 4: design and manufacturing of high-performance SiC power modules

- WP 5: global system and use case optimization.

The IRT will mainly work in LOTS 3, 4 and 5 with the following contributions (see Figure 3):

- WP 3: feedback from the SICRET project relating to the characterization of SiC power transistors

- WP 4: strong synergy with the SICRET + project, continuation of the SICRET project, relating to the study of SiC power modules. Expertise on the characterization and modeling of losses in SiC power modules.

- WP 5: expertise on the characterization and optimization of the traction chain, synergy with the Repowerdrive project relating to the optimization of the complete traction chain taking into account electromagnetic compatibility constraints.

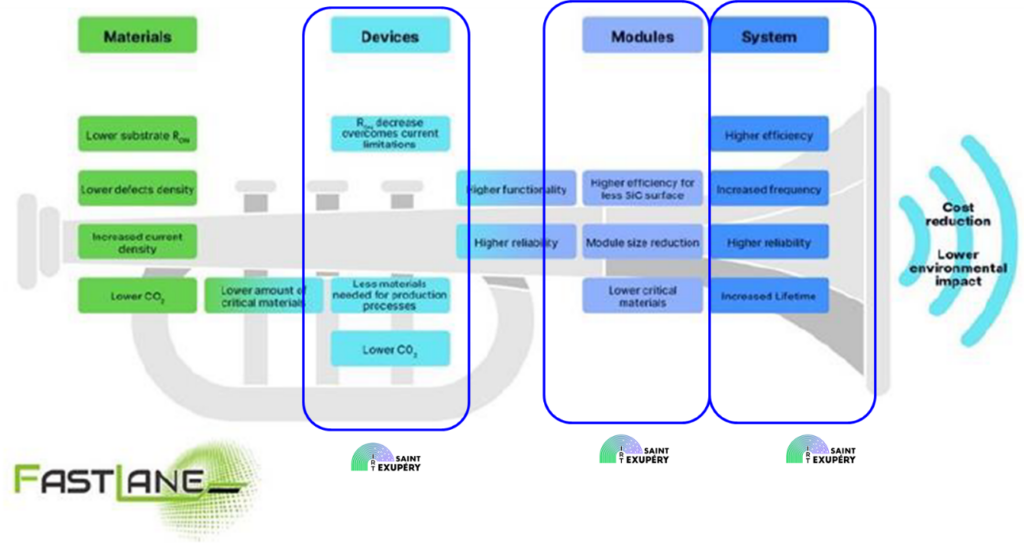

The general philosophy of the project is to improve the value chain of SiC technology by maximizing the value of European stakeholders while aiming to reduce the cost and environmental footprint of SiC technology.

This is why a transversal LCA WP, Life Cycle Analysis, will aim to prove the reduction of the environmental footprint of the new SiC technologies developed in FASTLANE compared to current SiC technologies, serving as baseline.

Funded by the European Union. Views and opinions expressed are however those of the author(s) only and do not necessarily reflect those of the European Union or Chips Joint Undertaking. Neither the European Union nor the granting authority can be held responsible for them.

The project is supported by the Chips Joint Undertaking (JU) and its members, including top-up funding by Austria, France, Germany, Romania, and Slovakia, under grant agreement No 101139788.